Design More Effective Power Factor Correction Using Wide Bandgap Semiconductors and Digital Control

Contributed By DigiKey's North American Editors

2020-10-14

Power factor correction (PFC) is necessary to maximize the efficiency of AC mains powered equipment including AC/DC power supplies, battery chargers, battery-based energy storage systems, motor drives, and uninterruptible power supplies. Its importance is such that there are regulations that dictate minimum power factor (PF) levels for specific types of electronic equipment.

To meet these regulations in the face of constant pressure to improve overall performance within ever-shrinking form factors, designers are turning to active PFC designs that take advantage of digital control techniques and wide bandgap semiconductors such as silicon carbide (SiC) and gallium nitride (GaN).

This article reviews PF concepts and definitions including differing definitions between the IEEE and the IEC and associated standards. It then introduces solutions for PFC from vendors such as STMicroelectronics, Transphorm, Microchip Technology, and Infineon Technologies that designers can use to implement PFC using wide bandgap semiconductors and digital control, including the use of evaluation boards.

What is power factor correction and why is it needed?

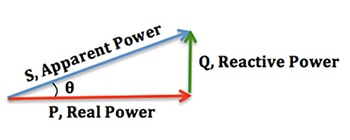

PF is a measure of the level of reactive power in a system. Reactive power is not true power but represents the impact of volts and amperes that are out of phase with each other (Figure 1). Since they are out of phase, they cannot contribute effectively to work, but still appear as a load to the AC mains supply line. The amount of reactive power in a system is one measure of the level of inefficiency of energy transfer. Active PFC uses power electronics to change the phase and/or shape of the current waveform drawn by a load to improve the PF. The use of PFC increases overall system efficiencies.

Figure 1: PF is defined as the cosine of θ and represents the ratio of real power absorbed by the load to the apparent power flowing in the circuit. The difference between the two is caused by the reactive power. As reactive power approaches zero, the load appears more purely resistive, the apparent power and real power become equalized, and the PF becomes 1.0. (Image source: Wikipedia)

Figure 1: PF is defined as the cosine of θ and represents the ratio of real power absorbed by the load to the apparent power flowing in the circuit. The difference between the two is caused by the reactive power. As reactive power approaches zero, the load appears more purely resistive, the apparent power and real power become equalized, and the PF becomes 1.0. (Image source: Wikipedia)

Poor PF can arise in linear or non-linear loads. Non-linear loads distort the voltage waveform or current waveform, or both. When non-linear loads are involved, it’s called distortion PF.

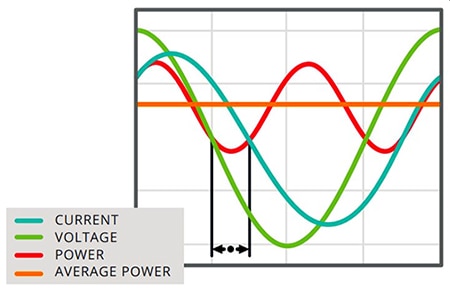

A linear load does not distort the shape of the input waveform but may change the relative timing (phase) between voltage and current due to its inductance and/or capacitance (Figure 2). Electrical circuits containing predominantly resistive loads (e.g., incandescent lamps and heating elements) have a PF of almost 1.0, but circuits containing inductive or capacitive loads (e.g., switch mode power converters, electric motors, solenoid valves, transformers, and lamp ballasts) can have a PF well below 1.0.

Figure 2: Instantaneous and average power calculated from AC voltage and current with a lagging PF—i.e., where the current lags the voltage—of 0.71 from a linear load. (Image source: CUI, Inc.)

Figure 2: Instantaneous and average power calculated from AC voltage and current with a lagging PF—i.e., where the current lags the voltage—of 0.71 from a linear load. (Image source: CUI, Inc.)

Most electronic loads are not linear. Examples of non-linear loads are switch-mode power converters and arc discharge devices such as fluorescent lamps, electric welding machines, or arc furnaces. Because current in these systems is interrupted by a switching action, the current contains frequency components that are multiples of the power system frequency. Distortion PF is a measure of how much the harmonic distortion of a load current decreases the average power transferred to the load.

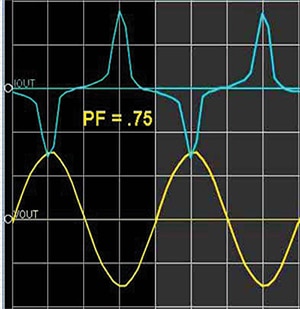

Figure 3: Sinusoidal voltage (yellow) and non-sinusoidal current (blue) give a distortion PF of 0.75 for this computer power supply, which is a non-linear load. (Image source: Wikipedia)

Figure 3: Sinusoidal voltage (yellow) and non-sinusoidal current (blue) give a distortion PF of 0.75 for this computer power supply, which is a non-linear load. (Image source: Wikipedia)

The difference between lagging and leading PF

A lagging PF denotes that the current lags (is behind) the voltage, and a leading PF denotes that the current leads (is ahead of) the voltage. For inductive loads (e.g., induction motors, coils, and some lamps), the current lags behind the voltage, producing a lagging PF. For capacitive loads (e.g., synchronous condensers, capacitor banks, and electronic power converters), the current leads the voltage, resulting in a leading PF.

The lagging or leading distinction does not equate to a positive or negative value. The negative and positive sign that precedes a PF value is determined by the standard used—either the IEEE or IEC.

PF and the IEEE versus the IEC

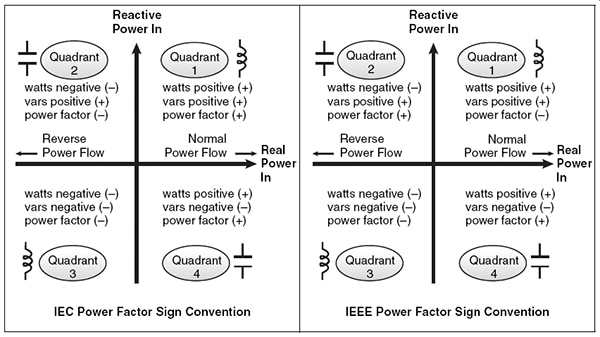

The diagrams in Figure 4 show the correlation between kilowatts (kW) of power, volt-ampere reactive (var) power, power factor, and inductive or capacitive loads for both the IEEE and IEC standards. Each organization uses different metrics to classify PF.

Figure 4: According to the IEC (left), the power factor sign is solely dependent on the direction of real power flow and is independent of the load being inductive or capacitive. According to the IEEE (right), the power factor sign is solely dependent on the nature of the load (that is capacitive or inductive). In this case, it is independent on the direction of real power flow. (Image source: Schneider Electric)

Figure 4: According to the IEC (left), the power factor sign is solely dependent on the direction of real power flow and is independent of the load being inductive or capacitive. According to the IEEE (right), the power factor sign is solely dependent on the nature of the load (that is capacitive or inductive). In this case, it is independent on the direction of real power flow. (Image source: Schneider Electric)

According to the IEC (left side of Figure 4), the PF sign is solely dependent on the direction of real power flow and is independent of the load being inductive or capacitive. According to the IEEE (right side of Figure 4), the PF sign is solely dependent on the nature of the load (that is capacitive or inductive). In this case, it is independent of the direction of real power flow. For an inductive load the PF is negative. For a capacitive load, the PF is positive.

PF standards

Regulatory authorities such as the EU have set harmonic limits to improve PF. To comply with current EU standard EN61000-3-2 (which is based on IEC 61000-3-2), all switched-mode power supplies with output power more than 75 watts must include PFC. 80 PLUS power supply certification by EnergyStar requires a PF of 0.9 or more at 100% of rated output power and requires active PFC. The latest edition of the IEC standard at the time of this writing is: IEC 61000-3-2:2018, “Electromagnetic compatibility (EMC) - Part 3-2: Limits - Limits for harmonic current emissions (equipment input current ≤16 A per phase).”

Uncorrected switch-mode power converters do not meet current PFC standards. One consideration that affects PF is what type of AC input is used: single phase or three phase. Single-phase uncorrected switching power supplies typically have a PF of about 0.65 to 0.75 (using the IEEE convention for PF sign described above). This is because most units use a rectifier/capacitor front end to make a DC bus voltage. This configuration only draws current at the peak of each line cycle, creating narrow, high pulses of current that result in poor PF (see Figure 3, above).

Three-phase uncorrected switch-mode power converters have a higher PF, often approaching 0.85 (also using the IEEE convention for PF sign). This is because even though a rectifier/capacitor is used to make a DC bus voltage, there are three phases that additively improve the overall PF. However, neither single nor three-phase switch-mode power converters can meet current PF regulations without the use of an active PF correction circuit.

Using WBG semiconductors and digital control to design active PFC

The use of digital control techniques and wide bandgap power semiconductors, including GaN and SiC, provide designers with new options for active PFC circuits that can deliver higher efficiencies and higher power densities compared with active PFC designs based on analog control or passive PFC designs.

Designers can replace analog controllers with advanced digital control techniques or supplement analog control with additional digital control elements, including microcontrollers, to achieve the maximum PFC performance. In some cases, WBG semiconductors can also be used to improve PFC performance.

Declining component cost has hastened implementation of two different methods for PFC: interleaved designs and bridgeless designs. Each approach brings a different set of benefits:

- Interleaved PFC benefits:

- Higher efficiency

- Improved heat distribution

- Reduced rms current through the PFC stage

- Modularity

- Bridgeless PFC benefits:

- Higher efficiency

- Halves the losses in the input rectification

- Improved heat distribution

- Higher power density

Three-channel interleaved PFC controller combines analog and digital control

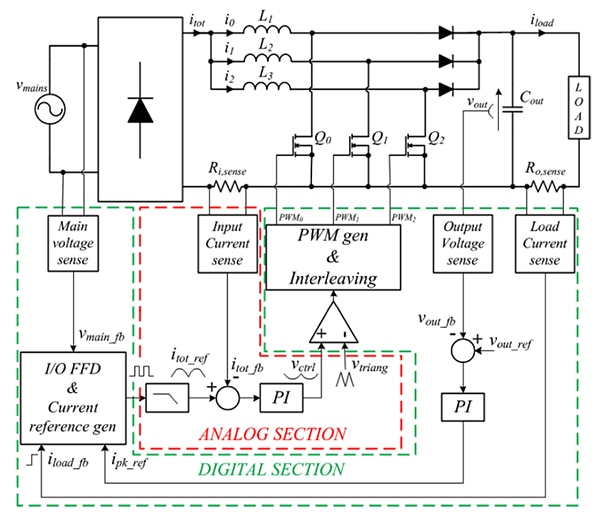

The STNRGPF01 controller from STMicroelectronics is a configurable ASIC that combines digital and analog control and can drive up to three channels in an interleaved PFC (Figure 5). The device works in continuous conduction mode (CCM) at fixed frequency with average current mode control and implements mixed signal (analog/digital) control. The analog inner current loop is performed by hardware, ensuring cycle-by-cycle regulation. The outer voltage loop is performed by a digital proportional-integral (PI) controller with fast dynamic response.

Figure 5: A functional block diagram of the STNRGPF01 shows the inner analog control section (red) and the outer digital control section (green) in a three-phase interleaved PFC application. (Image source: STMicroelectronics)

Figure 5: A functional block diagram of the STNRGPF01 shows the inner analog control section (red) and the outer digital control section (green) in a three-phase interleaved PFC application. (Image source: STMicroelectronics)

The STNRGPF01 implements a flexible phase shedding strategy that enables the correct number of PFC channels based on the actual load condition. With this function, the STNRGPF01 is always able to guarantee the highest power efficiency across a wide range of load current requirements.

The controller implements several functions: inrush current control, soft start-up, burst mode cooling management, and status indication. It also features a full set of embedded protections against overvoltage, overcurrent, and thermal faults.

To help designers get started, STMicroelectronics also offers the STEVAL-IPFC01V1 3 kW PFC power management evaluation board based on the STNRGPF01 (Figure 6). Features and specifications include:

- Input voltage range: 90 to 265 VAC

- Line frequency range: 47 to 63 Hertz (Hz)

- Maximum output power: 3 kW at 230 volts

- Output voltage: 400 volts

- PF: >0.98 at 20% load

- Total harmonic distortion: <5% at 20% load

- Mixed-signal control

- Switching frequency: 111 kilohertz (kHz)

- Cycle-by-cycle regulation (analog current control loop)

- Input voltage and load feed-forwards

- Phase shedding

- Burst-mode operation

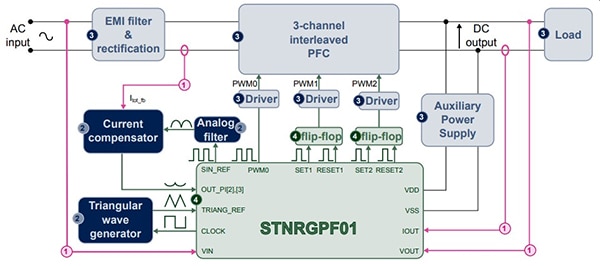

Figure 6: STEVAL-IPFC01V1 block diagram showing: 1. I/O measurement signals; 2. Analog circuitry; 3. Power stage; 4. Digital control section with STNRGPF01 digital controller; in a three-phase interleaved PFC. (Image source: STMicroelectronics)

Figure 6: STEVAL-IPFC01V1 block diagram showing: 1. I/O measurement signals; 2. Analog circuitry; 3. Power stage; 4. Digital control section with STNRGPF01 digital controller; in a three-phase interleaved PFC. (Image source: STMicroelectronics)

In addition to the STNRGPF01 mixed signal controller, this evaluation board includes STW40N60M2 N-channel, 600 volt, 34 ampere (A) low Qg silicon power MOSFETS and PM8834TR gate driver ICs.

Bridgeless totem pole PFC with GaN FETs

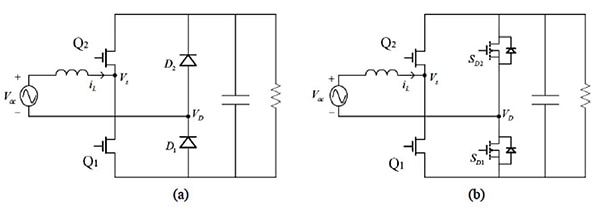

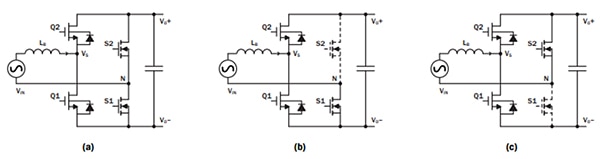

Bridgeless PFC topologies were developed to eliminate the voltage drops and inefficiencies associated with the use of diode bridge rectification. Bridgeless totem pole PFCs have been enabled by the emergence of WBG power semiconductors such as GaN and SiC (Figure 7). In a conventional totem pole design (a), two GaN FETs and two diodes are used for the line rectification. In a bridgeless totem pole modification (b), the diodes are replaced by two low resistance silicon MOSFETs to replace the diodes’ current-voltage (IV) drops to improve efficiency.

Figure 7: Two GaN FETs and two diodes are used for the line rectification in a conventional totem pole design (a); in a modified circuit (b), the diodes are replaced by two low resistance silicon MOSFETs to replace the diodes’ current-voltage drops to improve efficiency in the bridgeless totem pole. (Image source: Transphorm)

Figure 7: Two GaN FETs and two diodes are used for the line rectification in a conventional totem pole design (a); in a modified circuit (b), the diodes are replaced by two low resistance silicon MOSFETs to replace the diodes’ current-voltage drops to improve efficiency in the bridgeless totem pole. (Image source: Transphorm)

The significantly smaller reverse recovery charge (Qrr) of the GaN high electron mobility transistors (HEMTs) compared to that of silicon MOSFETs makes bridgeless totem pole designs practical (Figure 8). In this simplified schematic of a totem-pole PFC in CCM the focus is on minimizing conduction losses.

Figure 8: Simplified schematic of a totem-pole PFC in CCM mode comprises two fast-switching GaN HEMTs (Q1 and Q2) operating at a high pulse width modulation frequency and act as a boost converter, and two very low resistance MOSFETs (S1 and S2) operating at a much slower line frequency (50Hz/60Hz). (Image source: Transphorm)

Figure 8: Simplified schematic of a totem-pole PFC in CCM mode comprises two fast-switching GaN HEMTs (Q1 and Q2) operating at a high pulse width modulation frequency and act as a boost converter, and two very low resistance MOSFETs (S1 and S2) operating at a much slower line frequency (50Hz/60Hz). (Image source: Transphorm)

The circuit comprises two fast-switching GaN HEMTs (Q1 and Q2) and two very low resistance MOSFETs (S1 and S2). Q1 and Q2 operate at a high pulse width modulation (PWM) frequency and act as a boost converter. S1 and S2 operate at a much slower line frequency (50 Hz/60 Hz) and function as a synchronized rectifier. The primary current path includes one fast switch and one slow switch only, with no diode drop. The role of S1 and S2 is that of a synchronized rectifier, as illustrated in 8(b) and 8(c). During the positive AC cycle, S1 is on and S2 is off, forcing the AC neutral line tied to the negative terminal to the DC output. The opposite applies for the negative cycle.

To allow CCM operation, the body diode of the slave transistor must function as a flyback diode for the inductor current to flow during dead time. The diode current, however, must quickly reduce to zero and transition to the reverse blocking state once the master switch turns on. This is the critical process for a totem-pole PFC, which with the high Qrr of the body diode of high-voltage Si MOSFETs, results in abnormal spikes, instability, and associated high switching losses. The low Qrr of the GaN switches allows designers to overcome this barrier.

Designers can study the circuit’s operation using Transphorm’s TDTTP4000W066C 4 kW bridgeless totem-pole PFC evaluation board. It uses the MA330048 dsPIC33CK256MP506 digital power plug-in module (PIM) from Microchip Technology as the controller. Very high efficiency single-phase conversion is achieved with Transphorm’s Gen IV (SuperGaN) TP65H035G4WS GaN FETs. Using Transphorm GaN FETs in the fast-switching leg of the circuit and low-resistance MOSFETs in the slow-switching leg of the circuit results in improved performance and efficiency.

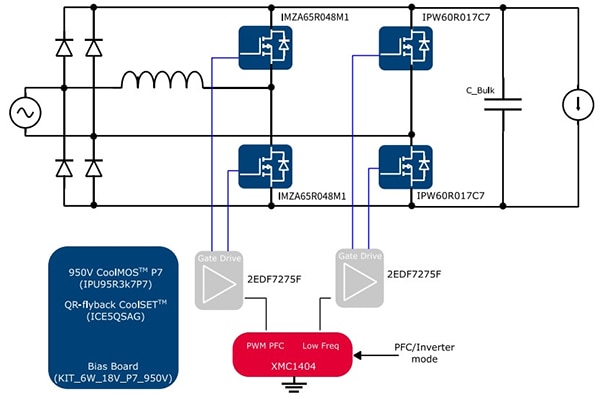

Bidirectional totem pole PFC combines silicon FETs and SiC FETs

For designers of grid-interactive battery electric vehicles and battery-based energy storage systems, Infineon offers the EVAL3K3WTPPFCSICTOBO1 evaluation board, a 3300 watt totem-pole PF corrector with bidirectional power capability (Figure 9). This bridgeless totem pole PFC board delivers a high power density of 72 watts per cubic inch. The totem pole implemented in the EVAL3K3WTPPFCSICTOBO1 board operates in CCM in both rectifier (PFC) and inverter mode, with full digital control implementation using the Infineon XMC1000 series microcontroller.

Figure 9: A block diagram of the EVAL3K3WTPPFCSICTOBO1 3300 watt totem-pole PFC evaluation board shows the topology that delivers the board’s specified 72 watt per cubic inch power density. (Image source: Infineon Technologies)

Figure 9: A block diagram of the EVAL3K3WTPPFCSICTOBO1 3300 watt totem-pole PFC evaluation board shows the topology that delivers the board’s specified 72 watt per cubic inch power density. (Image source: Infineon Technologies)

This totem pole PFC uses a combination of Infineon’s IMZA65R048M1 64 milliohm (mΩ), 650 volt, CoolSiC SiC MOSFETs and its IPW60R017C7 17 mΩ, 600 volt, CoolMOS C7 silicon power MOSFETs. The converter operates exclusively at high line (176 volts rms minimum, 230 volts rms nominal) in CCM with a 65 kHz switching frequency and achieves efficiency up to 99% at half load. Additional Infineon devices used in this 3300 watt bi-directional (PFC/AC-DC and inverter/AC-DC) totem-pole solution include:

- 2EDF7275FXUMA1 isolated gate drivers

- ICE5QSAGXUMA1 QR flyback controller with an IPU95R3K7P7 950 volt CoolMOS P7 MOSFET for the bias auxiliary supply

- XMC1404 microcontroller for PFC control implementation

Conclusion

A low PF introduces inefficiencies in the utility grid and in power converters, making PFC necessary for a variety of AC mains powered equipment, with regulations dictating minimum PF levels for specific types of electronic devices. To meet these regulatory requirements while also addressing the need for smaller form factors and increased performance, designers need an alternative to simple and low-cost passive PFC techniques.

As shown, designers can instead implement active PFC designs using digital control techniques and WBG semiconductors such as SiC and GaN to achieve higher PFs and more compact designs.

Recommended Reading

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.